Prosedur Percobaan

- Buatlah rangkaian seperti pada gambar berikut

- Buatlah kondisi switch-switch seperti pada jurnal yang telah disediakan

- Catat kondisi logika LED H0 & H1 nya.

Gambar 1. Rangkaian Flip-Flop

Gambar 2. Ouput

Gambar 3. Input

1 1. Apa perbedaan toggle dan clock?

Jawab:

Clock merupakan inputan berupa logika 0 dan 1. Clock merupakan penginputan yang berlangsung secara otomatis.

Toggle adalah suatu input berupa switch yang pada rangkaian berfungsi untuk memberikan logika ‘1’ dan ‘0’ atau ON/OFF bergantian dan secara manual.

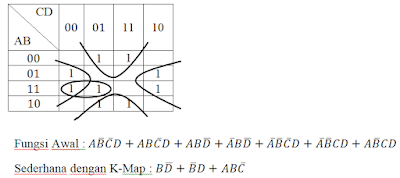

2 2. Sederhanakan Fungsi dibawah ini menggunakan Karnaugh Map !

Jawab :

- Bandingkan hasil yang didapat untuk masing-masing flipflop JK dan D, berdasarkan teori.

Kondisi 1

Pada kondisi ini, hanya B1 yang on, sesuai dengan tabel kebenaran JK Flipflop, B1 dan B0 yang dihubungkan dengan gerbang NOT, dan B1 terhubung dengan pin S, dan B0 terhubung dengan pin R. Karena B1 dan B0 masing-masing berlogika 1 dan 0, diinvert menjadi 0 dan 1. sehingga JK fliflop dalam keadaan reset. dan output (Q) akan berlogika 0, dan Q invers akan bernilai sebaliknya.

Sama seperti JK flipflop, keadaan D flipflop juga dalam keadaan reset, sehingga output Q berlogika 0, dan Q invers berlogika sebaliknya.

Kondisi 2

Pada kondisi ini, hanya B0 yang on, dan sesuai dengan tabel kebenaran dari Jk flipflop, yang telah dijelaskan pada poin sebelumnya, B0 yang berlogika 1 dan B1 yang berlogika 0 diinvert menjadi 0 dan 1. sehingga pin S diberikan logika 1, dan pin reset berlogika 0. sehingga JK flipflop dalam keadaan set, sehingga output (Q) berlogika 1, dan Q invers akan bernilai sebaliknya.

Seperti JK flipflop, keadaan D flipflop juga dalam keadaan reset, sehingga output Q berlogika 1, dan Q invers berlogika sebaliknya.

Kondisi 7

Pada kondisi ini, B6 dan B5 dilepaskan, B1, B2, B4, B0 berlogika 1, dan diberikan clock pada B3, sehingga JK flipflop dalam keadaan toogle, dan output yang sebelumnya dibalikkan. Q = 0 menjadi Q = 1. Dan D-flipflop off.

- File HTML [Download]

- Video Praktikum [Download]

Tidak ada komentar:

Posting Komentar